# Lifting Based 2D DWT Architecture for JPEG 2000

Jitendra Kumar Singh, Rakesh Patel, Ashish Singhadia

**Abstract** — In this thesis work, study and simulation has been carried out of a memory-efficient pipeline architecture which performs the twodimensional discrete wavelet transform. Normally the memory size used by two-dimensional architecture mostly depends on the pipeline registers of (1-D) DWT. In this project work, the data path can be reduced with the help of the lifting-based DWT algorithm and high performance pipeline architecture. Efficient pipeline architecture and efficient multiplier can enhance performance and speed of processing of 2D DWT architecture for jpeg 2000 as compare to any other low performance direct implemented pipeline architectures. The merits of the lifting based DWT techniques is to divide into low pass and the high pass filters into a sequence of lower and upper triangular matrices. The given 2-D DWT architecture is composition of two 1-D processors (column-wise, row wise). Finally, the given architecture (2-D DWT architecture) implements both 9/7and 5/3 filters with the help of cascade the three key components. In this work, 12 bit floating point multiplier and a Baugh Wooley multiplier is simulated, which require less memory and do the fast multiplication. By replacing the 1D DWT architecture's multiplier with this multiplier a less memory and a lower delay 1D DWTarchitecture can be obtained.

Index Terms— 2-D (two-dimensional), CSA (Carry Save Adder tree), DWT(Discrete Wavelet Transform, IO(input, output), JPEG (Joint Photographic Experts Group), RAM(Random Access Memory), RPA (recursive pyramid algorithm).

\_\_\_\_\_

# **1** INTRODUCTION

he two-dimensional Discrete Wavelet Transform (DWT) L has been very useful and applied in mostly image compression techniques. The Discrete Wavelet Transform (DWT) is being mostly used for image coding process. This is because of that DWT supports features like by resolution, region of interest coding, progressive image transmission by quality ease of compressed image manipulation, etc. One major drawback of the conventional convolution based Discrete Wavelet Transform DWT is, it requires a lot of computations. The wavelet transform decompose the signals into different different sub-bands and produces both time and frequency information which supports methods for analysing various signals. Many areas such as image analysis, digital signal processing and communication used DWT techniques. the demand for heavy internal memory requirements and realtime performance are the main issues for hardware implementation . The 2-D DWT can generally realized by separable approach, which splits the 2-D DWT implementation into two 1D operations (columnwise and rowwise filtering)and nonseparable approach .From 1990 to 2014 there are number of research work carried out in this area. K.K.Parthi and T.Nishantani present a combined (folded) architecture and digital-serial architecture to minimize the register and latency [5]. M.Vishwanath design a systolic parallel architecture to perform the recursive pyramid algorithm (RPA) with less storage and short latency [14].

A less computationally intensive lifting-based DWT architecture [2] is used to carry out the bi orthogonal wavelet filtering. The computational complexity can be reduced effectively by the factorizing conventional filter banks into many lifting steps. The memory prerequisite of lifting-based DWT [[1]] can also be reduce as compare to the convolutional DWT, based on the line-based architecture [[5]].The lifting scheme involves lower memory and less computation, the irregular and longer data paths are the main limitations for efficiency of hardware implementation.

The lifting based scheme for the 2D-DWT helps in overcome drawback and has been chosen in the JPEG2000 standard. JPEG 2000 [[6]] is the coding system and an image compression standard and it was created by the committee of Joint Photographic Experts Group in 2000, with a newly designed, wavelet-based methodology. With the help of advance, fast and less memory required multiplier, speed of operation can be increases which require less memory space. The Baugh-Wooley multiplication algorithm has been developed in order to design regular multiplier which is an efficient way to handle the sign bits. This technique, suited for 2'scompliment number. Baugh-Wooley multiplier is the paramount known algorithm (for signed multiplication) which is Two's compliment Signed multipliers, because it permit all the partial products to have positive signbits and maximizes the regularity of the multiplier.

The rest of this paper organised as follow. Section briefly introduces Lifting-Based and modified Lifting-Based Discrete Wavelet Transform. Third section introduces Baugh-Wooley multiplier which is main focused area in this paper. In fourth section Experiment and Result. In fifth section conclusion. Experimental results demonstrate that the Baugh Wooley Multiplier circuit improves the accurate performance, reduces the complexity of hardware and also reduces power consumption.

Jitendra kumar singh is currently pursuing masters degree program in Embedded system and VLSI design engineering in TIET Jabalpur, RGTU University, India, PH-09907796261. E-mail: jitendra.sinngjbp@gmail.com

<sup>•</sup> Rakesh patel is Asst.Professor in Electronics and comunication engineering in TIET Jabalpur, RGTU University, India , PH-09826886882. E-mail: rakeshpatel@takshshila.org

Ashish Singhadia is Asst. Professor in Electronics and comunication engineering in ,RKDF University,Bhopal, India , PH-08982469442. E-mail: singhadiaashish@gmail.com

### 2 PROPOSED METHODOLOGY

# a-Primitive Lifting-Based DWT-

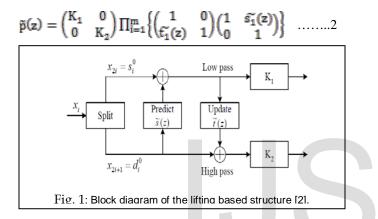

The lifting-based DWT is first derived by Daubechies and Sweldens [7]. The lifting scheme, splits DWT filter bank into many lifting steps. Fig 1 shows a block diagram of the lifting-based structure. The g (z) and h (z) are the high-pass and low-pass analysis filters. The poly-phase matrix  $\tilde{p}(z)$  is defined by this equation:

$$\widetilde{p}(z) = \begin{bmatrix} \widetilde{h}_{e}(z) & \widetilde{h}_{o}(z) \\ \widetilde{g}_{e}(z) & \widetilde{g}_{o}(z) \end{bmatrix} \dots \dots (1)$$

The polyphase matrix  $\tilde{\mathbf{p}}(z)$  can be factorized into a constant diagonal matrix of the primitive lifting-based structure multiplied by a sequence of alternat lower and upper triangular matrices.

Where K1 and K2 are the scaling factors, and s (z) and p (z) are the prediction and update operators respectively and n is the lifting step. The 9/7 filter has one scaling step and two lifting steps while the 5/3 filter can be regarded as aspecial case with single lifting step. The detailed forward algorithm of the 9/7 filter is described by wavelet coefficients si(low-pass coefficients) and di(high-pass coefficients) can be obtained.

Splitting Step: (i)

$$d_i^0 = x_{2i+1}$$

(3)

(First)

$$\mathbf{d}_{i}^{1} = \mathbf{d}_{i}^{0} + \alpha \times (\mathbf{s}_{i}^{0} + \mathbf{s}_{i+1}^{0})$$

. (Predictor) (5)

$$\mathbf{s}_{i} = \mathbf{s}_{i} + \mathbf{\beta} \times (\mathbf{d}_{i-1} + \mathbf{d}_{i}) \quad \text{(Updater)} \quad (6$$

(Second)

$$\mathbf{d}_{i} = \mathbf{d}_{i} + \gamma \times (\mathbf{s}_{i} + \mathbf{s}_{i+1})$$

(Predictor) (7)

$$\mathbf{s}_{i}^{*} = \mathbf{s}_{i}^{*} + \boldsymbol{\delta} \times (\mathbf{d}_{i-1}^{*} + \mathbf{d}_{i}^{*}) . (\text{Updater})$$

(8)

$$\mathbf{d}_{\mathbf{i}} = \mathbf{K}_{\mathbf{1}} \times \mathbf{d}_{\mathbf{i}}^{2} \tag{9}$$

$$\mathbf{s}_i = \mathbf{K}_1 \times \mathbf{s}_i^2 \tag{10}$$

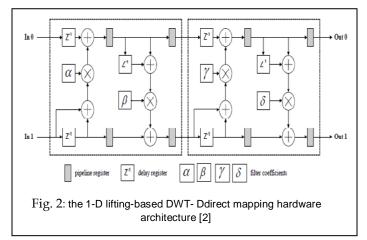

Several architectures have been projected to implement the lifting structures of the 5/3 and 9/7 filters. Fig. 2 depicts the 1-D liftingbased, direct mapping hardware architecture [2] for the 1-D lifting-based DWT. The required four stages of pipeline used to reduces the processing time, but the vital path is still limited by the computation of predictor or updater. Which are two adders and one multiplier propagation delay. Moreover, it require 32 pipeline registers to reduce the critical path to one multiplier delay.

b- Modified Lifting-Based Discrete Wavelet Transform

Since the predictor or updater reduces the critical timing delay, we combine the predictor and updater stages in a single lifting step. By combine (5) into (6), the lifting step will be expressed as one equation and each operation is performed by multiplication or addition as follows:

$$s_{i}^{1} = s_{i}^{0} + \beta \times \{ [d_{i-1}^{0} + \alpha \times (s_{i-1}^{0} + s_{i}^{0})] + [d_{i-1}^{0} + \alpha \times (s_{i}^{0} + s_{i+1}^{0})] \} ...$$

$$s_{i}^{1} = s_{i}^{0} + (\beta \times d_{i-1}^{0} + \beta \alpha s_{i-1}^{0} + \beta \alpha s_{i}^{0}) + (\beta d_{i-1}^{0} + \beta \alpha s_{i}^{0} + \beta \alpha s_{i+1}^{0}) ...$$

(11)

.....(11)

In the second lifting step, Eq. (7) substitutes into Eq. (8) as the first lifting step. While the outputs of the first step of lifting are  $s_1^2$ and  $Bd_1^1$  a factor  $\beta$  is derived to let the output  $Bd_1^1$  from the first lifting step can be obtained directly. In this adjustment, Eq. (11) has the same form as Eq. (12), which indicates that the two lifting steps can be realized in the same architecture. The second lifting step equations are written as follows:

$$\begin{split} s_{i}^{2} &= s_{i}^{1} + \delta \times (d_{i-1}^{0} + d_{i}^{0}), \\ s_{i}^{2} &= s_{i}^{1} + \delta \times \{ [d_{i-1}^{1} + \gamma \times (s_{i-1}^{1} + s_{i}^{1})] \\ + [d_{i}^{1} + \gamma \times (s_{i}^{1} + s_{i+1}^{1})] \}, \\ s_{i}^{2} &= s_{i}^{1} + (\frac{\nu}{n} \times \beta d_{i-1}^{1} + \delta \gamma \times s_{i-1}^{1} + \delta \gamma s_{i}^{1}), \\ + (\frac{\nu}{n} \times \beta d_{i}^{1} + \delta \gamma \times s_{i}^{1} + \delta \gamma \times s_{i+1}^{1}), \\ s_{i}^{2} &= s_{i}^{1} + (\frac{\nu}{n} \times \beta d_{i-1}^{1} + \delta \gamma \times s_{i-1}^{1} + \delta \gamma s_{i}^{1}), \\ + (\frac{\nu}{n} \times \beta d_{i}^{1} + \delta \gamma \times s_{i}^{1} + \delta \gamma \times s_{i+1}^{1}), \end{split}$$

(12)

The scaling step is finally represented as follows:

The above equations need six multipliers coefficient  $\beta$ ,  $\beta\alpha$ , -,  $\delta\gamma$ ,  $\stackrel{\mathbf{n}_{\underline{n}}}{=}$ ,  $\mathbf{K}_{\underline{n}}$  to perform the lifting and scaling steps. The primitive and modified algorithms have the equal number of multipliers. Moreover, the modified algorithm provides the lengthy computation data path of both the predictor and updater such that the arithmetic property can be performed and used some more efficiently. The inverse transform may be modified in the similar manner as the other case like forward case. The inverse transform begin from the

IJSER © 2014 http://www.ijser.org International Journal of Scientific & Engineering Research, Volume 5, Issue 11, November-2014 ISSN 2229-5518

scaling step.

$$s_i^2 = K_1^{-1} \times s_i$$

(15)

$d_i^2 = K_2^{-1} \times d_i$  (16)

The predictor and updater can be combined into a single equation, as shown in Eq. (3.17). By substituting  $\mathbf{s}_i^2 = \mathbf{K}_1^{-1} \times \mathbf{s}_i$  into the  $\mathbf{s}_i^2$  term, a new multiplier term,  $\gamma \mathbf{K}^{-1}$  is derived. It also reduces one multiplication operation for the input sequence  $\mathbf{s}_i$ .

$$\begin{aligned} d_{i}^{1} &= d_{i}^{2} - \gamma \times (s_{i}^{1} + s_{i+1}^{1}), \\ d_{i}^{1} &= d_{i}^{2} - \gamma \times \{ [s_{i}^{2} - \delta \times (d_{i-1}^{2} + d_{i}^{2}] + [s_{i+1}^{2} - \delta \times (d_{i}^{2} + d_{i+1}^{2})] \} \\ d_{i}^{1} &= d_{i}^{2} - (\gamma K_{1}^{-1} \times s_{i} - \gamma \delta \times d_{i-1}^{2} + \gamma \delta \times d_{i}^{2}) - (\gamma K_{1}^{-1} \times s_{i+1} - \gamma \delta \times d_{i}^{2} + \gamma \delta \times d_{i+1}^{2}) ]. \end{aligned}$$

Similarly, a factor  $\gamma$  is derived such that  $d_{i}^1$ ,  $\gamma s_i^1$  can be get directly. The equations are rewritten as follows:

$$d_{i}^{0} = d_{i}^{1} - \alpha \times (s_{i}^{0} + s_{i+1}^{0}).$$

(18)

$$d_{i}^{0} = d_{i}^{1} - \alpha \times \{[s_{i}^{1} - \beta \times (d_{i-1}^{1} + d_{i}^{1})] + [s_{i+1}^{1} - \beta \times (d_{i}^{1} + d_{i+1}^{1})]\},$$

$$d_{i}^{0} = d_{i}^{1} - \overset{\sim}{-} \times \{[\gamma s_{i}^{1} - \gamma \beta \times (d_{i-1}^{1} + d_{i}^{1})] + [\gamma s_{i+1}^{1} - \gamma \beta \times (d_{i}^{1} + d_{i+1}^{1})],$$

$$d_{i}^{0} = d_{i}^{1} - (\overset{u}{-} \times \gamma s_{i}^{1} - \alpha \beta \times d_{i-1}^{1} - \alpha \beta \times d_{i}^{1})],$$

$$(19)$$

TABLE 1

Coefficients Represented in the Binary Forms(the 9/7 Filter)

| FORWA             | RD COEF            | FICIENTS                        | INVERSE COEFFICIENTS          |                    |                                 |  |

|-------------------|--------------------|---------------------------------|-------------------------------|--------------------|---------------------------------|--|

| Coeffi-<br>cients | Value              | Absolute<br>value by<br>12 bits | Coeffi-<br>cients             | Value              | Absolute<br>value by<br>12 bits |  |

| вα                | 0.083984<br>375    | .0001010<br>11000               | γK <sub>1</sub> <sup>-1</sup> | 0.54296<br>875     | .10001011<br>0000               |  |

| (δ/β)>>1          | -4.18554<br>46875  | 100.0010<br>11111               | (δγ) <sub>≫1</sub>            | 0.19555<br>6640625 | .00110010<br>0001               |  |

| (δγ)>>1           | 0.195556<br>640625 | .0011001<br>00001               | ( <sup>α</sup> /γ)»1          | 898193<br>359375   | .11100101<br>1111               |  |

| (K2/δ)>>1         | 5.546875           | 101.1000<br>11000               | (βα) <sub>≫1</sub>            | 0.04199<br>21875   | .00001010<br>1100               |  |

| (K1)<<1           | 1.625488<br>28125  | 1.101000<br>00001               | $(\alpha^{-1})_{\ll 2}$       | -2.5214<br>84375   | 10.100001<br>0110               |  |

Finally, to reconstruct the even part of the data, the coefficient  $\alpha^{-1}$  is applied to bring back the output  $\mathbf{s}_{i}^{0}$

$$\mathbf{s}_i^0 = \boldsymbol{\alpha}^{-1} \times \mathbf{s}_i^0 \tag{20}$$

Both modified and primitive IDWT algorithms have constant six multipliers. In the modified case, the six constant multipliers are  $K_2 \stackrel{-1}{}_{,\gamma} \gamma K_1 \stackrel{-1}{}_{,\gamma} \gamma \delta$ ,  $\stackrel{=}{=}_{,\alpha\beta}$ , and  $\alpha^{-1}$ . To avoid the instance of run over, the huge absolute coefficients,  $\gamma \delta$  and  $\delta / \alpha$ , can be further scaled. In TABLE 1 coefficients in binary form of forward and inverse transform is shown. Although larger scaling factors can decrease the overflow instances, the overall finite word length precision would be decreased significantly. The quality values of coefficients are depending on both the 8-bit raw data and 12-bit data coefficients specified in TABLE 1.

# C- 2D DWT Overall Architecture

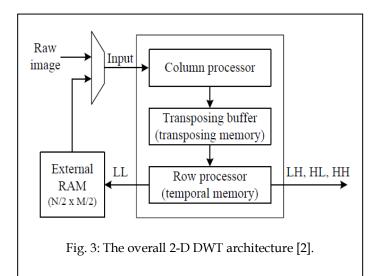

The given architecture performs the forward and inverse 2-D DWT transform in the column-row fashion. Fig. 3 depicts the overall 2-D DWT architecture, which includes three main components — the column processor, the transposing buffer and the row processor. To carry out the one-level decomposition for an NxM image, the given architecture executes the column processor, the transposing buffer and the row processor simultaneously, where N and M represent the image height and width. Moreover, the row processor has to execute row-wise transform once enough column processed data are obtained to decrease the internal memory size. Thereafter, the MN/4size external RAM is used to store the LL band output coefficients for the next level decomposition.

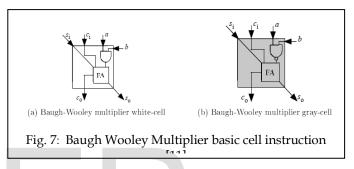

# **D** - Baugh Wooley Multiplier

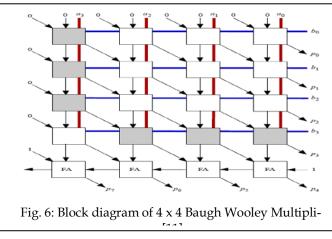

Baugh-Wooley is Two's compliment Signed multipliers, which is the best known multiplier algorithm for signed mul-

tiplication as it maximizes the reliability of the multiplier and allow all of the partial products tp provide positive sign bits and it avoid having deal with the negatively weighted bits .The Baugh-Wooley multiplication algorithm which was developed to design for Two's compliment number's direct multipliers .When two's compliment numbers direct multiplying, each of the partial products of multiplication to be added is a signed numbers. Therefore each partial product must be sign (for signed multiplication) extended to the width of the final product in order to structure a correct sum by the Adder CSA(Carry Save Adder tree). According to efficient method Baugh-Wooley approach, of count additional entries to the bit matrix recommended to keep away from using with the negatively weighted bits in the partial product matrix for multiplication.

In fig 4 is partial product arrays of 5\*5 bits Unsigned & fig 5 is partial product arrays of 5\*5 bits Signed bits are shown:

|       |                                           |              |              |              | a4                    | <i>a</i> <sub>3</sub> | $a_2$        | $a_1$     | $a_0$     |   |

|-------|-------------------------------------------|--------------|--------------|--------------|-----------------------|-----------------------|--------------|-----------|-----------|---|

|       |                                           |              |              |              | <i>x</i> <sub>4</sub> | <i>x</i> <sub>3</sub> | $x_2$        | $x_1$     | $x_0$     |   |

|       |                                           |              |              |              | $a_4 x_0$             | $a_{3}x_{0}$          | $a_{2}x_{0}$ | $a_1 x_0$ | $a_0 x_0$ | _ |

|       |                                           |              |              | $a_4 x_1$    | $a_3 x_1$             | $a_2 x_1$             | $a_1 x_1$    | $a_0 x_1$ |           |   |

|       |                                           |              | $a_{4}x_{2}$ | $a_{3}x_{2}$ | $a_{2}x_{2}$          | $a_1 x_2$             | $a_{0}x_{2}$ |           |           |   |

|       |                                           | $a_4 x_3$    | $a_{3}x_{3}$ | $a_{2}x_{3}$ | $a_1 x_3$             | $a_0 x_3$             |              |           |           |   |

|       | $a_4 x_4$                                 | $a_{3}x_{4}$ | $a_{2}x_{4}$ | $a_1 x_4$    | $a_{0}x_{4}$          |                       |              |           |           |   |

| $p_9$ | $p_8$                                     | $p_{7}$      | $p_6$        | $p_5$        | P 4                   | $p_3$                 | $p_2$        | $p_1$     | $p_0$     |   |

|       | Fig. 4; 5*5 unsigned multiplications [12] |              |              |              |                       |                       |              |           |           |   |

|                                         |           |               |               |               | a4                    | $a_3$                 | $a_2$     | $a_1$     | $a_0$     |

|-----------------------------------------|-----------|---------------|---------------|---------------|-----------------------|-----------------------|-----------|-----------|-----------|

|                                         |           |               |               |               | <i>x</i> <sub>4</sub> | <i>x</i> <sub>3</sub> | $x_2$     | $x_1$     | $x_0$     |

|                                         |           |               |               |               | $-a_{4}x_{0}$         | $a_3 x_0$             | $a_2 x_0$ | $a_1 x_0$ | $a_0 x_0$ |

|                                         |           |               |               | $-a_{4}x_{1}$ | $a_3 x_1$             | $a_2 x_1$             | $a_1 x_1$ | $a_0 x_1$ |           |

|                                         |           |               | $-a_{4}x_{2}$ | $a_{3}x_{2}$  | $a_{2}x_{2}$          | $a_1 x_2$             | $a_0 x_2$ |           |           |

|                                         |           | $-a_{4}x_{3}$ | $a_{3}x_{3}$  | $a_{2}x_{3}$  | $a_1 x_3$             | $a_0 x_3$             |           |           |           |

|                                         | $a_4 x_4$ | $-a_{3}x_{4}$ | $-a_2 x_4$    | $-a_1x_4$     | $-a_0 x_4$            |                       |           |           |           |

| $p_9$                                   | $p_8$     | $p_7$         | $p_6$         | $p_5$         | $p_4$                 | $p_3$                 | $p_2$     | $p_1$     | $p_0$     |

| Fig. 5: 5*5 signed multiplications [12] |           |               |               |               |                       |                       |           |           |           |

Experimental result demonstrate that the Baugh Wooley Multiplier circuit improves the accurate performance, reduces the complexity of hardware and also reduces power consumption that is dynamic power 15.3mW and the required maximum clock period of 3.912ns which is very efficient and reliable as compared to the reference paper

# **3 EXPERIMENT AND RESULT**

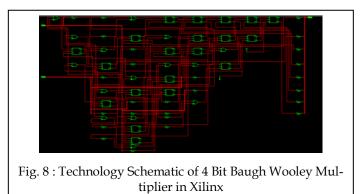

This section deals with the simulation of Column Processor, Row Processor, Transposing Buffer, Floating Point Multiplier and Baugh Wooley Multiplier in XILINX ISE Simulator as well as in MATLAB showing the 2nd level decomposition of image on application of 2D- DWT. The overall time obtain by Baugh Wooley Multiplier

Is 197 ns and memory requirement 1674 KB, Normally other multiplier gets more than 500ns. This is much lesser than other multiplier. Experimental result demonstrate that the Baugh Wooley Multiplier circuit improves the accurate performance, reduces the complexity of hardware and also reduces power consumption that is dynamic power 15.3mW and the required maximum clock period of 3.912ns which is very efficient and reliable as compared to the reference paper.

International Journal of Scientific & Engineering Research, Volume 5, Issue 11, November-2014 ISSN 2229-5518

Simulation of Column Processor, Row Processor, Transposing Buffer, Floating Point Multiplier are easy to design in this thesis work our main focus on Baugh Wooley Multiplier which is shown in fig. 08 in XILINX ISE Simulator .

| 🔥 MATLAB 7.8.0 (R2009a)                                                                                                                                                                                                                           |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| File Edit Debug Parallel Desktop Window Help                                                                                                                                                                                                      |  |  |  |  |  |  |

| : 🖺 🗃 👗 🐂 🖏 🤊 🕅 👪 🗃 🖹 🛛 🧶 Current Directory: C:\Users\user\Documents                                                                                                                                                                              |  |  |  |  |  |  |

| Shortcuts 🗷 How to Add 🖪 What's New                                                                                                                                                                                                               |  |  |  |  |  |  |

| Command Window                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| New to MATLAB? Watch this <u>Video</u> , see <u>Demos</u> , or read <u>Getting Started</u> .                                                                                                                                                      |  |  |  |  |  |  |

| <pre>&gt;&gt; %COLUMN PROCESSOR EQUATION SIMULATION &gt;&gt; s1=[1 3 5 7 9] ; c=[13 ]; s0=[0 1 3 5 7] ; d0= [0 2 4 6 8]; &gt;&gt; b=[11 ] ; s2= [3 5 7 9 11] ; d1=[2 4 6 8 10] ; &gt;&gt; f=(b*s2 + d1*c+b*s1) + s1 + (b*s0 + c*d0 + b* s1)</pre> |  |  |  |  |  |  |

| f =                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 82 213 355 497 639                                                                                                                                                                                                                                |  |  |  |  |  |  |

| <pre>&gt;&gt; %ROW PROCESSOR EQUATION SIMULATION &gt;&gt; m1=[14]; s2= [3 5 7 9 11]; d1=[2 4 6 8 10]; s1=[1 3 5 7 9]; &gt;&gt; m2=[32]; s0=[0 1 3 5 7]; d0= [0 2 4 6 8]; &gt;&gt; f=(m1*s2 + d1*m2+m1*s1) + s1 + (m1*s0 + m2*d0 + m1* s1)</pre>   |  |  |  |  |  |  |

| f =                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 135 363 605 847 1089                                                                                                                                                                                                                              |  |  |  |  |  |  |

| ∫x >> \$END                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Fig.9: Result of CP and RP equation (12) simulation in MATLAB                                                                                                                                                                                     |  |  |  |  |  |  |

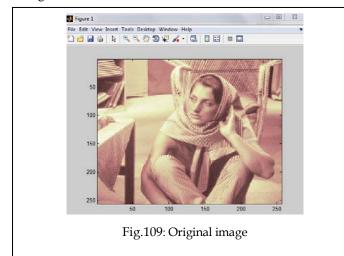

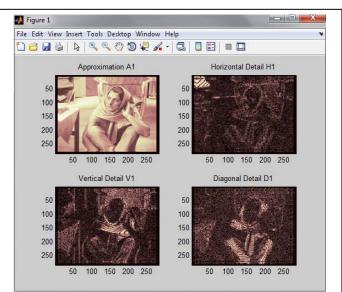

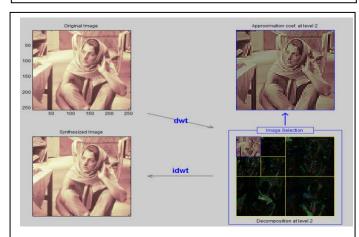

(2) Simulation Results in MATLAB of 2D DWT of an image. Then in fig 11 shown the 4 different configuration of image LL,HL,LH and HH.

In fig 12 there is a compaision between original and compressed image. And fig 13 shows the DWT and inverse DWT of image.

Fig. 11: Displaying the Approximation and Details of image

Fig. 12: Displaying the original and compressed image

Fig. 13: Displaying the forward DWT and inverse DWT of image, using GUI in MATLAB

FPGA Requirement -

## **FPGA Requirement of Five Main Entities**

| ENTITY              | CELLS USAGE |         | MEMORY  | PRO-    |

|---------------------|-------------|---------|---------|---------|

|                     | ELEMENTS    | NO.S    | USAGE   | CESSING |

|                     |             | OF      |         | TIME    |

|                     |             | ELEMENT |         | TAKEN   |

| FLOATING            | BELs        | 706     | 170400  | 250 ns  |

| POINT<br>MULTIPLIER | FF/LD       | 54      | KB      |         |

| MULTIFLIEK          | IO          | 61      |         |         |

|                     | BUFFERS     |         |         |         |

| COLUMN              | BELs        | 1463    | 178848  | 410 ns  |

| PROCESSOR           | FF/FD       | 168     | KB      |         |

|                     | IO          | 61      |         |         |

|                     | BUFFERS     |         |         |         |

|                     | TRISTATE    | 48      |         |         |

|                     | BUFFERS     |         |         |         |

| TRANSPOS-           | BELs        | 706     | 167000  | 220 ns  |

| ING BUFFER          | IO          | 73      | KB      |         |

|                     | BUFFERS     |         |         |         |

|                     | TRISTATE    | 1       |         |         |

|                     | BUFFERS     |         |         |         |

| ROW PRO-            | BELs        | 1463    | 178848  | 410 ns  |

| CESSOR              | FF/FD       | 168     | KB      |         |

|                     | IO          | 61      |         |         |

|                     | BUFFERS     |         |         |         |

|                     | TRISTATE    | 48      |         |         |

|                     | BUFFERS     |         |         |         |

| BAUGH               | BELs        | 67      | 1674 KB | 197 ns  |

| WOOLEY              | FF/FD       | 0       |         |         |

| MULTIPLIER          | IO          | 16      |         |         |

|                     | BUFFERS     |         |         |         |

|                     | TRISTATE    | 0       |         |         |

|                     | BUFFERS     |         |         |         |

# 4. CONCLUSION

The Discrete Wavelet Transform provides a representation of signals with multi resolution. The transform can be implemented using filter banks. This report presents the simulation work for column processor, transposing buffer and row processor of 2D DWT architecture for JPEG 2000 and the study of high-performance and low-memory pipeline architecture for 2-D lifting-based DWT of the 5/3and 9/7 filters. By merging the predictor and updater into one single step, we can derive efficient pipeline architecture [2]. Hence, given the same number of arithmetic units, the given architecture has a shorter pipeline data path .In this thesis, architectures for the Lifting based DWT have been implemented. For each of them, parameters such as memory requirement and speed were discussed. The simulation results verify the functionality of the design. The proper scheduling of the wavelet coefficients to the Transposing Buffer ensures that, when the coefficients are

finally read back from the Transposing Buffer, they are available in the required order for further processing by Row Processor. The proposed architecture [2] is simple since further levels of decomposition can be achieved using identical processing elements. The architecture provides parallel processing with fast computation of DWT . It has low memory requirements as compare to other and consumes very low power.

# 5. ACKNOWLEDGMENT

I Jitendra Kumar Singh wish to thank Prof.Rakesh Patel and Prof. Ashish Singhadia.

# 6. REFERENCES

- X.Lan, N. Zheng and Y.Liu," Low-power and high-speed VLSI architecture for lifting-based forward and inverse wavelet transform", IEEE Transactions on Consumer Electronics, Vol. 51, No. 2, pp. 379- 385, July 2005.

- [2] B Wu and C. Lin, "A high performance and memory efficient pipeline architecture for the 5/3 and 9/7 discrete wavelet transform of JPEG2000 codec", IEEE Trans. On Circuits and Systems for Video Technology, Vol. 15, No. 12, pp. 1615-1628, April 2005.

- [3] C. Christopoulos, A. Skodras and Ebrahimi, "The JPEG2000 still image coding system: an overview, IEEE Trans. On Consumer Electronics, Vol. 4, No. 4, pp.1103 – 1127, July 2000

- [4] T. Acharya and P. Tsai, "JPEG2000 Standard for Image Compression Concepts, Algorithms and VLSI Architectures", Wiley Inter science – a John Wiley & Sons, June2005.

- [5] K.K. Parhi and T. Nishitani, "VLSI architectures for discrete wavelet transforms," IEEE Trans. on VLSI Syst., vol.1, pp.191-202, June 1993.

- [6] Andra, K., Chakrabarti, C., and Acharya, T.: "A high performance JPEG 2000 architecture", IEEE Trans. on Circuits Syst. for Video Technol., vol. 8 , No. 9, pp. 209–218, June 2003.

- [7] I. Daubechies and W. Sweldens, "Factoring wavelet transform into lifting steps," The J. of Fourier Analysis and Applications, vol.4, pp.247-269, April 1998.

- [8] G. K. Wallace, "The JPEG Still Picture Compression Standard", IEEE Trans. On Consumer Electronics, Vol. 38, No 1, Feb. 1992.

- [9] W. Sweldens, "The new philosophy in bi orthogonal wavelet constructions," in Proc. SPIE, vol.2569, pp.68-79, 1995.

- [10] S.-C. B. Lo, H. Li and M.T. Freedman, "Optimization of wavelet decomposition for image compression and feature preservation," IEEE Trans. on Medical Imaging, vol.22, pp.1141-1151, September 2003.

- [11] H. Liao, M. Kr. Mandal and B.F. Cockburn, "Efficient architectures for 1-D and 2-D lifting-based wavelet transforms," IEEE Trans.on Signal Processing, vol. 52, no. 5, pp. 1315-1326, May 2004.

- [12] Sjalander, M. Larsson-Edefors, P., 'High-speed and low-power multipliers using the Baugh-Wooley algorithm and HPM reduction tree', IEEE Trans. On Electronics, Circuits and Systems, p.p 33-36, September 2008

- [13] Tu.S.H.-L., Chih-Hung Yen, "A High-Speed Baugh-Wooley Multiplier Design Using Skew-Tolerant Domino Techniques", IEEE Trans. On Circuits and Systems, p.p. 598-601, May 2006.

- [14] M. Vishwanath,"The recursive pyramid algorithm for the discreat wavelet transform "IEEE Trans. Signal Process vol. 42, no.3, pp-673-676. March 1994